exynos4412�ȴ����

�r�g��2018-08-16 ��Դ��δ֪

exynos4412�ȴ����

�r�g��2018-08-16 ��Դ��δ֪

�W�����M���_�l�r���������ȴ��@�K���Ɇ������挢ʹ��exynos4412оƬ���A���_�l��(fs4412)���������v�⡣

ʹ�õ����փ����£�

FS4412_CoreBoard_V2.pdf

FS4412-DevBoard-V5.pdf

SEC_Exynos4412_Users Manual_Ver.1.00.00.pdf

����

exynos4412�惦������K��

iROM�������R��^����������A�õij���Ҳ��bl0

iRAM ���Ȳ��ȴ�^�����dͨ�^OM�x���Ć��ӳ���ͨ�����dbl1��bl2

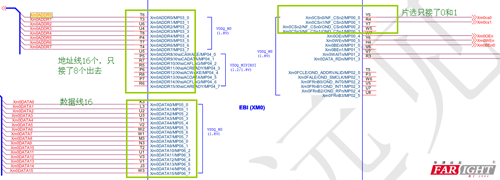

SMC���o�B�ȴ�^��Static Read Only Memory Controller ��ͨ������ӳ���ⲿ�������O�䣬��W���ȣ�ԓ�^�֞�4��bank��ÿ��16M(����Ӳ���փ�xm0�_�^��)

SFR������ܼĴ����^��ͨ������ӳ��SOC�Ȳ��O�䣬��GPIO��

DMC���ӑB�ȴ�^�������҂�ͨ�����x�ϵăȴ档

ps���ӑB�ȴ�(���ڄӑB�ȴ汾������늣���Ҫ����ˢ�£����攵�������ԽЄӑB�ȴ�)(����Ӳ���փ�xm1��xm2�_�^��)

Ӳ��ԭ��(SMC)

Exynos4412����1��������SMC,�֞�4��bank

�]���е�ַ���е�ַ������оƬ���Ãȴ��С��2^8bit=256/16=16Byte

�ⲿ�O��Ƭ�x�r��ֻ���x0����1.

Ӳ��ԭ��(DMC)

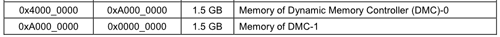

Exynos4412���Ѓɂ�������DRAM���������քe��DMC0��DMC1,���Խ�2�M��ͬ��DDR�ȴ档DMC0��DMC1�քe֧�ִ�1.5GB��DRAM��������֧��DDR2/DDR3��LPDDR2�ȣ�512 Mb, 1 Gb, 2 Gb, 4 Gb and 8 Gbit�ăȴ��O�䣬֧��16/32bit��λ����DRAM0 �����ĵ�ַ��0x4000_0000~0xAFFF_FFF��1.5GB��DRAM1 �����ĵ�ַ��0xA000_000~0x0000_0000��1.5GB��

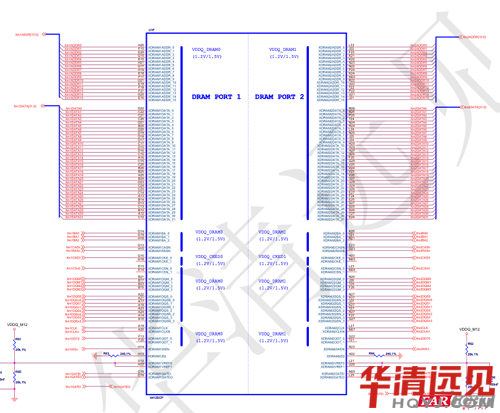

4412��1GB��DRAM����4Ƭ��С��256M*16��DDR3оƬ�M�϶���(�鿴оƬ��̖���Եõ�)

оƬ��̖��K4B4G1646B-HYXX

��һλ: K��ʾ�ȴ�

�ڶ�λ��4��ʾfalsh��� DRAM

����λ��B��ʾDDR3

��4~5λ. Density(ע�����H��λ��ԓ��bit��������Byte)���҂�����4Gbit=4G/16(����λ)=256MByte

��6~7λ. organization�����������_�������҂�����16

������ɣ��_�l���Ϲ���4Ƭ�@�ӵăȴ�оƬ������������256M*4=1G

�@��ƬDDR оƬ���ֳ��˃Ƀ�һ�M���M��32λ��������Ƭ���ǒ�ӵ�DMC0̎

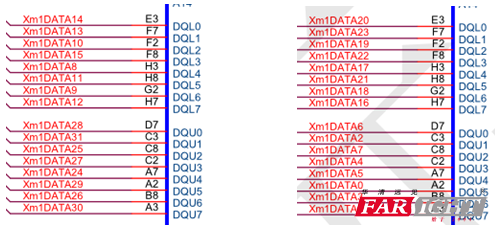

���D���£�

�ֽ�D����(ֻ����һ��)��

���σɈD���Կ������@��ƬDDR оƬ���ֳ��˃Ƀ�һ�M���M��32λ��������Ƭ���ǒ�ӵ�DMC0̎�����£�

· ��߅һƬ16λ����߅16λ���M��32λ����

· ȫ��оƬƬ�x�쵽CS0��

· bank������

3·��(BA0-BA2)����2^3�M�ϣ�Ҳ����һ��оƬ�ϣ�bank��8��

· ��ַ��

��ַ������15(A0-A14)

ps��һ��оƬ�ȴ��֧�֣�2^(bank����+��ַ��)=2^33=8Gbit/16=512MByte

· ���е�ַ��

nRAS��nCAS�����õ�ַ���к����x��ͬһ�r��ֻ����һ�N��ַ��ʹ��(�����о�����)���҂��İ�����оƬ��256M(2^28)��28-3(bank)-15(�е�ַ)=10(�е�ַ)

· ��ַ����

�@����������ǣ���Ƭ�x��CS���ͣ�Ȼ��RAS���͕r����ʾ���^�����е�ַ����A0-A14��15λ;��CAS���͕r����ʾ���^�������е�ַ����A0-A9���е�ַ��Ď�λ���A�����Á�Uչ�ȴ棬һ��оƬ�ȴ����ԔUչ��512M��

�ȴ愝�ֶ���bankԭ��

����DDR�Dz��Ԃ����·�ģ����ԣ�ÿ��һ�Εr�g���ȴ�������͕�ˢ��һ���·��Ҳ����Ҫ��һ��늣����ֻ��һ��Bank����ô�Y��������ijһ�r�̣�Ҫô����늣�Ҫô������늡�

�������@�ӷֳ���8��Bank�����Ҍ�000��늵ĕr����߀������010����ʣ�µĄe��Bank���xȡ�������@�Ӿ͜pС�˵ȴ��ĕr�g�������f���·ˢ�r�������xȡ�����ˡ�

exynos�����ϣ�ÿ��bank��С= 256M/8=32M(1��оƬ����2^3��bank)

�ȴ�Ӌ�㷽��

SDRAM����Ӌ��

Ӌ��Ɍ�ַ��Ԫ�Ĕ���(32λ)

��ַ����(���_��)��11(A0-A10)

bank������2(BA0-BA1) ���ԽM�ϳ�2^2�� bank

���о���=211(�����ַ���ľ�̖��11�����_�����M����211�N)

���о���=211(�����ַ���ľ�̖��11�����_�����M����211�N)

һ��bank�п���Ԫ��=211x 211

оƬ�п���Ԫ��=(bank����)×(һ��bank�п���Ԫ��)

= 22 x 211 x 211

= 224

��ע��

����о��c�о��ς�ݔ�Ĕ����ǽ��^���a(�M�Ϸ�ʽ)�ģ�������ֱ�ӵ���̖����̖��

Ҳ�����fÿ��bank����213 ���к� 29 ���У�����ֻ��13�к�9�С�

����Ҫ��ַ�Ć�Ԫ�ڵ�(2�о����� )�У���( 2�о�����)�С�

����bank0���������0 0000 0010 0000���������0 0000 1000��

��˼��Ҫ�@ȡ��32����8�Ć�Ԫ�Ĕ�������������5����3�Ĕ�����

����о������� 0 0010 1101 0110���о�������0 0011 1010����˼�ǫ@ȡ��726����58�Ć�Ԫ�Ĕ�����

����һ��32MB��SDRAMоƬ����4��Logic-bank(߉bank)��λ��16bit(��ÿ����Ԫ��16bits)����ַ��13�l�����о���13�����о���9��Ӌ��ã�

һ��bank�Ć�Ԫ��= 213 x 29= 4194304(��4M)��

оƬ����Ԫ��=4Banks × 4M units = 16M units ��

оƬ��λ��=16M units × 16bits/per_unit = 256M bits ��

оƬ���ֹ���=256M bits/8 = 32M Bytes ��

�ȴ��ʼ������

�������ṩ�Ĕ����փԡ�SEC_Exynos4412_Users Manual_Ver.1.00.00���ĵ�1046��ṩ�o��һ���P��LPDDR2-S4�ij�ʼ�����E��LPDDR2��ʾ����DDR2��DDR3�ij�ʼ���^�̑����@��һ�ӣ��҂��Ͱ��@���^�́���ʼ��DDR3

��ʼ�����̣����փ��� 18.3.1 LPDDR2-S4 ������

18.3.1 LPDDR2-S4

Use the sequence given here to initialize LPDDR2 devices. Unlessspecified otherwise, these steps are

mandatory. Note that the memory CK/CKn must be less than or equal to50 MHz before you initialize the

LPDDR2-S4 device.

1. DMC must assert and holdCKE to a logic low level to provide stable power for memory device and thenapply

stable clock.

2. Set thePhyControl0.ctrl_start_point and PhyControl0.ctrl_inc bit-fields to a correctvalue according to clock

frequency. Set the PhyControl0.ctrl_dll_on bit-field to"1" to activate the PHY DLL.

3. DQS cleaning: Set thePhyControl1.ctrl_shiftc and PhyControl1.ctrl_offsetc bit-fields to theappropriate value

according to clock frequency, board delay, and memory tDQSCKparameter.

4. Set thePhyControl0.ctrl_start bit-field to "1".

5. Set the ConControl. Atthis moment, an auto-refresh counter should be disabled.

6. Set the MemControl. Atthis moment, all power down modes should be disabled.

7. Set the MemConfig0register. When there are two external memory chips, set the MemConfig1register.

8. Set the PrechConfig andPwrdnConfig registers.

9. Set the TimingAref,TimingRow, TimingData, and TimingPower registers according to memory AC

parameters.

10. Set the QosControl0 to 15and QosConfig0 to 15 registers when a certain bus master requires QoS scheme.

11. Wait for thePhyStatus0.ctrl_locked bit-fields to change to "1". Verify whetherPHY DLL is locked.

PHY DLL compensates the changes of delay amount that pressure,volume, and temperature variation

causes during memory operation. Therefore, you should not power offPHY DLL for reliable operation.

It can be in power-off mode except when it runs at low frequency.When you use the power-off mode,

set the PhyControl0.ctrl_force bit-field to the correct valueaccording to the PhyStatus0.ctrl_lock_value[9:2]

bit-field for fix delay amount. Clear the PhyControl0.ctrl_dll_onbit-field to turn off PHY DLL.

12. Set thePhyControl1.fp_resync bit-field to "1" to update DLL information.

13. Confirm that Clock Enable(CKE) is in a logic low level at least 100ns after power on.

14. Issue a NOP command byusing the DirectCmd register to assert and hold CKE to a logic high level.

15. Wait for a minimum of 200ms.

16. Issue a MRS command byusing the DirectCmd register to reset memory devices and program the operating

parameters.

17. Wait for minimum of 1 μs.

18. Issue a MRR command byusing the DirectCmd register to poll the DAI bit of the MRStatus register.

This is to know whether or not Device Auto-Initialization iscomplete.

19. If there are two externalmemory chips, execute step 14 to 19 for chip1 memory device.

20. Set the ConControl toturn on an auto-refresh counter.

21. Set MemControl registerwhen you require power-down modes.

���g����IJ��E:

1��DMC���ܱ���O�ã�����Ҫ����CKE����ƽ���Ա�����ṩ�������Դ�͕r犽oDDR

2�������r��l���O��PhyControl0.ctrl_start_point ��PhyControl0.ctrl_inc bit-fields�������O��PhyControl0.ctrl_dll_on bit-field �� "1" �ц���PHY DLL��

3��DQS ����������r��l�ʡ������ӕr��оƬ��tDQSCK�����O��PhyControl1.ctrl_shiftc ��PhyControl1.ctrl_offsetcbit-fields��

4���O�� PhyControl0.ctrl_start bit-field ��"1"��

5���O��ConControl���˕r������ʹ���Ԅ�ˢ��Ӌ����(auto-refresh counter )��

6. �O��MemControl���˕r�����е�power downģʽ���P�]��

7���O��MemConfig0 �Ĵ������������Ѓ�Ƭ�惦оƬ�r���O��MemConfig1�Ĵ�����

8���O�� PrechConfig�� PwrdnConfig�Ĵ�����

9������DDR3�� AC�����O��TimingAref, TimingRow, TimingData, �� TimingPower�Ĵ�����

10����������������ҪQoS�r���r���O��QosControl0 ��15�Ĵ�����QosConfig0 �� 15�Ĵ�����

11���ȴ� PhyStatus0.ctrl_locked bit-fields ׃�� "1"���Դ_�� PHY DLL �Ƿ��i����PHY DLL �����a���������w�e?�͜ضȵȭh����׃���������оƬ�������g���҂������P�]��PHY DLL���Դ��ֻ�Ю����ڵ͵ĕr��l�ʕr�ſ����ГQ��Power-off ģʽ�����҂���power-off ģʽ������PhyStatus0.ctrl_lock_value[9:2]���ӕr�������O��PhyControl0.ctrl_forcebit-field�����PhyControl0.ctrl_dll_on bit-field���P�] PHY DLL��

12���O��PhyControl1.fp_resync bit-field �� "1" ������ DLL���O�á�

13���_�����Դ��늺����ٱ���Clock Enable (CKE)�ڵ��ƽ100ns��

14����DirectCmd �Ĵ��������һ�lNOPָ���ұ���CKE ����ƽ��

15�����ٵȴ�200us��

16���l��MRSָ��������O�ô惦оƬ�IJ���������

17�����ٵȴ�1us��

18����MRRָ�����ԃMRStatus�ļĴ�����DAIλ�����@�����_���Ԅӳ�ʼ���^���Ƿ���ɡ�

19������ⲿ�Єe�Ĵ惦оƬ���؏͈���14��19�����O��оƬ1��

20���O��ConControl�톢��auto-refresh counter.

21�����҂�Ҫ�M��power-downģʽ���O��MemControl�Ĵ�����

������߅�IJ��E���O�þͿ������DDR�ij�ʼ����

����exynos4412�ȴ�������}