╚A×ķöy╩ųAltera╣▓═¼čą░l(f©Ī)2.5DĘŌčb╝»│╔FPGA║═ā╚(n©©i)┤µå╬į¬

üĒį┤Ż║elecfans

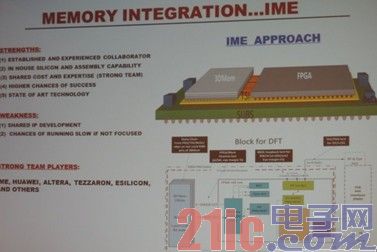

×ķ┤“ŲŲ═©ėŹŽĄĮy(t©»ng)ā╚(n©©i)┤µÄ¦īÆŽ▐ųŲŻ¼╚A×ķ║═Alteraīó║Ž┴”čą░l(f©Ī)ęį2.5DĘŌčbą╬╩Į╝»│╔FPGA║═ā╚(n©©i)┤µå╬į¬ĪŻ╚A×ķę╗╬╗┘Y╔Ņ┐ŲīW(xu©”)╝ę▒Ē╩ŠŻ¼▀@ĒŚ(xi©żng)╝╝ąg(sh©┤)ļm╚╗╝¼╩ųŻ¼Ą½╩Ūį┌ŠW(w©Żng)Įj(lu©░)ųąģs╩Ū╩«ĘųĻP(gu©Īn)µIĄ─ĪŻ▀@ę╗Ž¹ŽóĄ─╣½▓╝Ż¼╩╣Ą├ų«Ū░ĻP(gu©Īn)ė┌╚A×ķ╗“╩╣ė├ASICČ°ī¦(d©Żo)ų┬Altera╣½╦Šžö(c©ói)äš(w©┤)ĀŅørśI(y©©)┐ā(j©®)▓╗╝čĄ─é„┬ä▓╗╣źūįŲŲĪŻ

ļmšfų╗ė├┴╦3éĆ(g©©)į┬Ż¼Ą½ą┬įO(sh©©)éõīó’@ų°Ąž£p╔┘ļŖ┬Ę░Õ┐šķgŻ¼▓ó╠ßĖ▀ąį─▄ĪŻ╚A×ķ├└ć°(gu©«)čą░l(f©Ī)┘Y╔Ņ┐ŲīW(xu©”)╝ęAnwar A. MohammedšfŻ¼Ī░2.5-D╣ĶųąĮķīė╦Ų║§╩Ū▀m║ŽŠW(w©Żng)Įj(lu©░)╣½╦ŠĄ─Ī¬Ī¬╩┬īŹ(sh©¬)╔ŽŻ¼╦¹éāę▓╩ŪĻP(gu©Īn)µI╦∙į┌ĪŻĪ▒

ę╗─ĻŪ░Ż¼Xilinxą¹▓╝Ųõį┌2.5-D╣ĶųąĮķīė╔Ž╩╣ė├ČÓ─Ż▓óąą╝╝ąg(sh©┤)Ą─├▄╝»FPGAĪŻ─ŪĢr(sh©¬)Ż¼Xilinxę▓ī”(du©¼)ŠW(w©Żng)Įj(lu©░)╣½╦ŠĄ─╝╝ąg(sh©┤)ėąśO┤¾Ą─┼d╚żŻ¼▓ó×ķ╬┤üĒīóFPGA║═┤µā”(ch©│)Ų„ėąą¦ĮY(ji©”)║ŽĄ─«a(ch©Żn)ŲĘū÷ėŗ(j©¼)äØĪŻ

į┌▀xō±2.5-D╣ĶųąĮķīėų«Ū░Ż¼╚A×ķ╗©┴╦1─ĻČÓĄ─Ģr(sh©¬)ķgŻ¼ė├┴╦▓╗Ž┬9ĘNĘĮĘ©üĒ“×(y©żn)ūCŲõą¦╣¹ĪŻ│²┴╦Altera═ŌŻ¼╚A×ķ▀ĆĖ·TezzaronĪóeSilicon║═ą┬╝ėŲ┬╬óļŖūė蹊┐╦∙Č╝ėą╦∙║Žū„ĪŻ(╚ńŽ┬łD╦∙╩Š)

ą┬2.5-DįO(sh©©)éõīó╚Ī┤·10ų┴20 DDR┤µā”(ch©│)Ų„ęį╝░─┐Ū░╚A×ķŽĄĮy(t©»ng)š²į┌╩╣ė├Ą─ASICŻ¼╣Ø(ji©”)╩Ī┴╦Į³18%Ą─ļŖ┬Ę░Õ┐šķg║═ā╔▒ČĄ─ĦīÆ/═▀ĪŻÅVĘ║Ą─I/OĮM╝■īóų¦│ų8éĆ(g©©)128╬╗Ū■Ą└;FPGAīó░³└©╚A×ķ▀ē▌ŗĪóPCI Express─ŻēKęį╝░ų┴╔┘3 Gbit / sĄ─SERDESµ£┬ĘĪŻ

Mohammedį┌ł¾(b©żo)ĖµųąÅŖ(qi©óng)š{(di©żo)Ż¼Ī░╬ęéāŠĆ┐©Ą─┤¾ąĪ╩Ū║ŃČ©Ą─Ż¼Ą½╩Ū╚ń╣¹─ŃŽļę¬░čįĮüĒįĮČÓĄ─╣”─▄╝»│╔ĄĮ╔Ž├µĄ─įÆŻ¼─Ūī”(du©¼)┤╦Č°čįŻ¼2.5D╩Ūę╗éĆ(g©©)║▄ÅŖ(qi©óng)┤¾Ą─╣żŠ▀ĪŻ╝┤╩╣│§╦³║▄░║┘FŻ¼Ą½╩ŪīóĖ³ČÓ╣”─▄╝»│╔į┌2.5D╣ĶųąĮķīė╔ŽīóĢ■(hu©¼)£p╔┘Øōį┌│╔▒ŠĪŻComms╣½╦Šę└┐┐Ė³┐ņĄ─┤«▓ó╩š░l(f©Ī)Ų„ęį╝ė╦┘é„╦═öĄ(sh©┤)ō■(j©┤)ų┴ā╚(n©©i)┤µĄ─╦┘Č╚Ż¼Ą½╩Ū┤«▓ó╩š░l(f©Ī)Ų„į÷ęµį┌ą┬╣ż╦ć╝╝ąg(sh©┤)Ž┬ģsĖ³┬²ĪŻ┼fĄ─ĮŌøQĘĮ░Ė▓╗į┘Ųū„ė├┴╦ĪŻĪ▒

Žļę¬ĮŌøQ2.5DįO(sh©©)éõå¢Ņ}Ż¼╚A×ķ║═Ųõ║Žū„╗’░ķ╚į╚╗├µī”(du©¼)ų°║▄ČÓĄ─╠¶æ(zh©żn)ĪŻ╣ĶųąĮķīė╚į╚╗▒╚▌^░║┘FŻ¼│╔▒Š─_ĄūĄ─▓Ż┴¦║═ėąÖC(j©®)▓─┴Ž▀Ćė├▓╗╔ŽĪŻ╣ż│╠Ĥéā?n©©i)▒╔┘║├Ą──ŻŠ▀Ī?.5D CAD╣żŠ▀ĪóūŃē“Ą─┐╔ą┼öĄ(sh©┤)ō■(j©┤)Īó£y(c©©)įć▓▀┬įĪóĘĄ╣ż║═¤ß╠Ä└Ē╣▄└ĒĄ╚ĪŻ

┤╦═ŌŻ¼2.5DĄ─╣®æ¬(y©®ng)µ£▀Ć▓╗ē“│╔╩ņŻ¼▀xō±ĘČć·▓╗┤¾ĪŻ┤╦═Ō═Č┘Y╗žł¾(b©żo)┬╩ę▓▓╗ŪÕ│■ĪŻMohammed▒Ē╩Šę╗Ūą│õØMų°╬┤ų¬Ż¼ŽŻ═¹┤¾╝ęę╗ŲĘųŽĒäō(chu©żng)ęŌ┤_▒Ż╝╝ąg(sh©┤)│╔╣”ĪŻĄ½Š═╦Ń▓╗│╔╣”Ż¼ę▓ø]╩▓├┤║├¾@ėĀĄ─Ż¼«ģŠ╣╬┤ų¬ę“╦ž╠½ČÓĪŻ2.5DĄ─ĘĮĘ©╩Ūė╔╣Ķ═©┐ūŽ“═Ļš¹3-DČč»BąŠŲ¼▐D(zhu©Żn)ūāĄ─ųąķg▓Į¾EĪŻ

¤ß³c(di©Żn)µ£ĮėŻ║

1ĪóAndroidäō(chu©żng)ą┬╦┘Č╚│¼╠O╣¹Ż║ąQ╩│iOS╩ął÷(ch©Żng)Ę▌Ņ~

2ĪóARM│╔╣”─µęuŻ¼╚½Ū“Ą┌ę╗┼_(t©ói)ARM│¼╝ē(j©¬)ėŗ(j©¼)╦ŃÖC(j©®)ķ_╣ż

3Īó╬ó▄øWin8ŪČ╚ļ╩ĮŽĄĮy(t©»ng)ŠĆ┬ĘłD╣½▓╝

4ĪóAOSPŻ║Android 4.2į┤┤·┤aęč╣½ķ_

5Īó╬ó▄øŅA(y©┤)ė[░µWin8ŪČ╚ļ╩ĮŽĄĮy(t©»ng)Į±╚šŲ╠ß╣®Ž┬▌d